# $\mathsf{C}\lambda\mathsf{as}\mathsf{H}$ From Haskell To Hardware

Christiaan Baaij & Matthijs Kooijman

September 3, 2009

Computer Architecture for Embedded Systems (CAES) group

Faculty of Electrical Engineering, Mathematics and Computer Science

University of Twente

.utwente.nl Enschede, The Netherlands

http://caes.ewi.utwente.nl

### What will we see?

- Small tour: what can we describe in  $C\lambda$ asH

- Quick real demo

Virtuele demo

### What is $C\lambda$ asH?

- C $\lambda$ asH: CAES Language for Hardware Descriptions

- Rapid prototyping language

- Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

- Rapid prototyping language

Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

- Wij zijn wij

- CλasH voor rapid prototyping

- Subset haskell vertaalbaar

- Mealy machine beschrijving

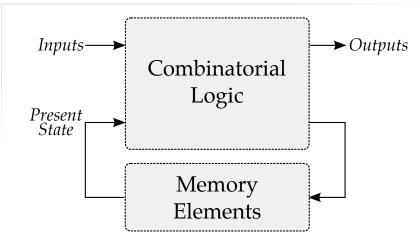

# Mealy Machine

Voor wie het niet meer weet, dit is een mealy machine

# Haskell Description

```

mealyMachine ::

InputSignals →

State →

(State, OutputSignals)

mealyMachine inputs state = (new_state, output)

where

new_state = logic state input

outputs = logic state input

```

# Haskell Description

```

mealyMachine ::

InputSignals →

State →

(State, OutputSignals)

mealyMachine inputs state = (new_state, output)

where

new_state = logic state input

outputs = logic state input

```

# Haskell Description

```

mealyMachine ::

InputSignals →

State →

(State, OutputSignals)

mealyMachine inputs state = (new_state, output)

where

new_state = logic state input

outputs = logic state input

```

# Simulating a Mealy Machine

```

run func state [] = []

run func state (i : input) = o : out

where

(state', o) = func i state

out = run func state' input

```

# Simulating a Mealy Machine

```

run func state [] = []

run func state (i:input) = o:out

where

(state', o) = func i state

out = run func state' input

```

# Simulating a Mealy Machine

```

run func state [] = []

run func state (i:input) = o:out

where

(state', o) = func i state

out = run func state' input

```

#### Small Use Case

- Small Polymorphic, Higher-Order CPU

- Each function is turned into a hardware component

- Use of state will be simple

Import all the built-in types, such as vectors and integers:

**import** CLasH.HardwareTypes

SHA LE

Import annotations, helps  $\mathsf{C}\lambda$ as $\mathsf{H}$  to find top-level component

import CLasH. Translator. Annotations

### **Imports**

Import all the built-in types, such as vectors and integers:

**import** CLasH.HardwareTypes

Import annotations, helps  $C\lambda$ asH to find top-level component:

**import** CLasH. Translator. Annotations

# Type definitions

#### First we define some ALU types:

**type**

$$Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a$$

**type**  $Opcode = Bit$

And some Register types:

$${f type}\ RegBank\ s\ a = Vector\ (s+D1)\ a$$

${f type}\ RegState\ s\ a = State\ (RegBank\ s\ a)$

And a simple Word type:

# Type definitions

#### First we define some ALU types:

**type**

$$Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a$$

**type**  $Opcode = Bit$

And some Register types:

**type**

$$RegBank \ s \ a = Vector (s + D1) \ a$$

**type**  $RegState \ s \ a = State (RegBank \ s \ a)$

And a simple Word type:

# Type definitions

#### First we define some ALU types:

**type**

$$Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a$$

**type** Opcode = Bit

#### And some Register types:

**type**

$$RegBank \ s \ a = Vector (s + D1) \ a$$

**type**

$$RegState s a = State (RegBank s a)$$

#### And a simple Word type:

# **Operations**

#### We make a primitive operation:

$$primOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$$

$primOp \ f \ a \ b = a \ f' \ a$

We make a vector operation:

vectOp ::

$$(a

ightarrow a

ightarrow a)

ightarrow Op s a$$

vectOp  $f$  a  $b$  = foldl  $f$  a  $b$

We support Higher-Order Functionality

# **Operations**

We make a primitive operation:

$$primOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$$

$primOp \ f \ a \ b = a \ f' \ a$

We make a vector operation:

$$vectOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$$

$vectOp \ f \ a \ b = foldl \ f \ a \ b$

■ We support Higher-Order Functionality

# **Operations**

We make a primitive operation:

$$primOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$$

$primOp \ f \ a \ b = a \ f' \ a$

We make a vector operation:

$$vectOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$$

$vectOp \ f \ a \ b = foldl \ f \ a \ b$

■ We support Higher-Order Functionality

# Simple ALU

#### We define a polymorphic ALU:

```

alu ::

Op \ s \ a \rightarrow

Op \ s \ a \rightarrow

Opcode \rightarrow a \rightarrow Vector \ s \ a \rightarrow a

alu op1 op2 Low a \ b = op1 \ a \ b

alu op1 op2 High a \ b = op2 \ a \ b

```

■ We support Patter Matching

# Simple ALU

#### We define a polymorphic ALU:

```

alu ::

Op \ s \ a \rightarrow

Op \ s \ a \rightarrow

Opcode \rightarrow a \rightarrow Vector \ s \ a \rightarrow a

alu op1 op2 Low a \ b = op1 \ a \ b

alu op1 op2 High a \ b = op2 \ a \ b

```

■ We support Patter Matching

# Register Bank

#### Make a simple register bank:

```

registerBank :: (Some\ context...) \Rightarrow (RegState\ s\ a) \rightarrow a \rightarrow RangedWord\ s \rightarrow RangedWord\ s \rightarrow Bit \rightarrow ((RegState\ s\ a), a) registerBank (State\ mem)\ data_in\ rdaddr\ wraddr\ wraddr\ wrenable = ((State\ mem'), data_out) \quad where data_out = mem\ !\ rdaddr\ mem' \ |\ wrenable \equiv Low = mem |\ otherwise = replace\ mem\ wraddr\ data_in

```

#### We support Guards

# Register Bank

#### Make a simple register bank:

```

registerBank :: (Some\ context...) \Rightarrow (RegState\ s\ a) \rightarrow a \rightarrow RangedWord\ s \rightarrow RangedWord\ s \rightarrow Bit \rightarrow ((RegState\ s\ a), a) registerBank (State\ mem)\ data_in\ rdaddr\ wraddr\ wrenable = ((State\ mem'), data_out) \quad \quad where \quad data_out = \ mem !\ rdaddr\ \quad mem' \quad wrenable \equiv Low = \ mem \quad otherwise \quad = replace\ mem\ wraddr\ data_in

```

#### We support Guards

# Simple CPU

#### Combining ALU and register bank:

```

\{-\#ANN\ actual\_cpu\ TopEntity\#-\}

actual\_cpu::

(Opcode, Word, Vector\ D4\ Word, RangedWord\ D9, RangedWord\ D9, Bit) 	o RegState\ D9\ Word 	o (RegState\ D9\ Word, Word)

actual\_cpu\ (opc, a, b, rdaddr, wraddr, wren)\ ram = (ram', alu\_out)

where

alu\_out = alu\ (primOp\ (+))\ (vectOp\ (+))\ opc\ ram\_out\ b

(ram', ram\_out) = registerBank\ ram\ a\ rdaddr\ wraddr\ wren

```

### Annotation is used to indicate top-level component

# Simple CPU

#### Combining ALU and register bank:

```

\{-\#ANN\ actual\_cpu\ TopEntity\#-\}

actual\_cpu::

(Opcode, Word, Vector\ D4\ Word, RangedWord\ D9, RangedWord\ D9, Bit) 	o RegState\ D9\ Word 	o (RegState\ D9\ Word, Word)

actual\_cpu\ (opc, a, b, rdaddr, wraddr, wren)\ ram = (ram', alu\_out)

where

alu\_out = alu\ (primOp\ (+))\ (vectOp\ (+))\ opc\ ram\_out\ b

(ram', ram\_out) = registerBank\ ram\ a\ rdaddr\ wraddr\ wren

```

Annotation is used to indicate top-level component

# Simple CPU

```

Combining ALU and register bank:

```

Annotation is used to indicate top-level component

- It can be used for more than toy examples

- We designed a matrix reduction circuit

- We simulated it in Haskell

- Simulation results in VHDL match

- Synthesis completes without errors or warnings

Swill a Live

- It can be used for more than toy examples

- We designed a matrix reduction circuit

- We simulated it in Haskell

- Simulation results in VHDL match

- Synthesis completes without errors or warnings

- It can be used for more than toy examples

- We designed a matrix reduction circuit

- We simulated it in Haskell

- Simulation results in VHDL match

- Synthesis completes without errors or warnings

- It can be used for more than toy examples

- We designed a matrix reduction circuit

- We simulated it in Haskell

- Simulation results in VHDL match

- Synthesis completes without errors or warnings

- It can be used for more than toy examples

- We designed a matrix reduction circuit

- We simulated it in Haskell

- Simulation results in VHDL match

- Synthesis completes without errors or warnings

- It can be used for more than toy examples

- We designed a matrix reduction circuit

- We simulated it in Haskell

- Simulation results in VHDL match

- Synthesis completes without errors or warnings

- No Effort: GHC API Parses, Typechecks and Desugars Haskel

- Hard.. sort of: Transform resulting Core, GHC's Intermediate Language to a normal form

- Easy: Translate Normalized Core to synthesizable VHDI

- No Effort: GHC API Parses, Typechecks and Desugars Haskell

- Hard.. sort of: Transform resulting Core, GHC's Intermediate Language to a normal form

- Easy: Translate Normalized Core to synthesizable VHDI

- No Effort: GHC API Parses, Typechecks and Desugars Haskell

- Hard.. sort of: Transform resulting Core, GHC's Intermediate Language, to a normal form

- Easy: Translate Normalized Core to synthesizable VHDI

- No Effort: GHC API Parses, Typechecks and Desugars Haskell

- Hard.. sort of: Transform resulting Core, GHC's Intermediate Language, to a normal form

- Easy: Translate Normalized Core to synthesizable VHDL

#### How do we use $C\lambda$ asH?

#### As a library:

- Import the module: CLasH.Translator

- And call makeVHDLAnnotations ghc\_lib\_dir [files\_to\_translate]

#### Customized GHC:

- Call GHC with the –vhdl flag

- Use the :vhdl command in GHCi

#### Real Demo

- We will simulate the small CPU from earlier

- Translate the CPU code to VHDL

- Simulate the generated VHDL

- Synthesize the VHDL to get a hardware schematic

### Some final words

- Still a lot to do: make a bigger subset of Haskell translatable

- Real world designs work

- We bring functional expressivity to hardware designs

See 1

# Complete signature for registerBank

```

registerBank ::

(NaturalT s

, PositiveT (s + D1)

, ((s + D1) > s) \sim True)) \Rightarrow

(RegState s a) \rightarrow a \rightarrow RangedWord s \rightarrow

RangedWord s \rightarrow Bit \rightarrow ((RegState s a), a)

```