# $\mathsf{C}\lambda\mathsf{asH}$ From Haskell To Hardware

#### Christiaan Baaij & Matthijs Kooijman

#### September 3, 2009

Computer Architecture for Embedded Systems (CAES) group Faculty of Electrical Engineering, Mathematics and Computer Science University of Twente wi.utwente.nl Enschede, The Netherlands

http://caes.ewi.utwente.nl

$C\lambda$ asH - From Haskell To Hardware

Man Law

CλasH 97-80-600-08-79

CλasH From Haskell To Hardware

Christiaan Baaij & Matthijs Kooijman

September 3, 2009

Computer Architecture for Embedded Systems (CAES) goo Faculty of Electrical Engineering, Mathematics and Computer Scien University of Twee Stay://caes.exi.utawate.al Encodeds, The Methedan

- Small tour: what can we describe in  $C\lambda$ asH

- Quick real demo

- CλasH: CAES Language for Hardware Descriptions

- Rapid prototyping language

- Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

- Jung and - Le

#### ■ CλasH: CAES Language for Hardware Descriptions

- Rapid prototyping language

- Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

States and

# ■ CλasH: CAES Language for Hardware Descriptions ■ Rapid prototyping language

- Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

Sea auto

#### ■ C $\lambda$ asH: CAES Language for Hardware Descriptions

- Rapid prototyping language

- Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

See a w

#### ■ C $\lambda$ asH: CAES Language for Hardware Descriptions

- Rapid prototyping language

- Subset of Haskell can be translated to Hardware (VHDL)

- Structural Description of a Mealy Machine

Ma a Li

ChasH: CAES Language for Hardware Descriptions

Rapid prototyping Language

Subset of Haskell can be translated to Hardware (VHDL)

Structural Description of a Meaky Machine

What is ClasH7

- We are a Computer Architectures group, this has been a 6 month project, no prior experience with Haskell.

- $C\lambda$ asH is written in Haskell, of course

- $C\lambda$ asH is currently meant for rapid prototyping, not verification of hardware desigs

- Functional languages are close to Hardware

- We can only translate a subset of Haskell

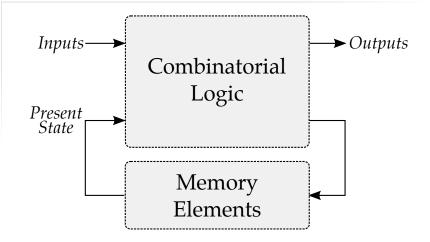

- All functions are descriptions of Mealy Machines

#### What again is a Mealy Machine?

$C\lambda$ asH - From Haskell To Hardware

Mealy machine bases its output on current input and previous state

#### Haskell Description

```

mealyMachine ::

InputSignals →

State →

(State, OutputSignals)

mealyMachine inputs state = (new_state, output)

where

new_state = logic state input

outputs = logic state input

```

Current state is part of the inputNew state is part of the output

#### Haskell Description

mealyMachine :: InputSignals → State → (State, OutputSignals) mealyMachine inputs state = (new\_state, output) where new\_state = logic state input outputs = logic state input

# Current state is part of the inputNew state is part of the output

#### Haskell Description

```

mealyMachine ::

InputSignals →

State →

(State, OutputSignals)

mealyMachine inputs state = (new_state, output)

where

new_state = logic state input

outputs = logic state input

```

Current state is part of the inputNew state is part of the output

Haskell Description

multiplications::

Insufficients::

Insufficients::

(Sate Comparizingents)

multiplications::

multiplications::

multiplication::

(Comparizingents)

multiplication::

(Comparizingent::

Comparizingent::

Current state is part of the input

New state is part of the output

- State is part of the function signature

- Both the current state, as the updated State

# Simulating a Mealy Machine

run func state [] = []

run func state (i : input) = o : out

where

(state', o) = func i state

out = run func state' input

#### State behaves like an accumulator

# Simulating a Mealy Machine

run func state [] = []

run func state (i : input) = o : out

where

(state', o) = func i state

out = run func state' input

#### State behaves like an accumulator

# Simulating a Mealy Machine

run func state [] = []

run func state (i : input) = o : out

where

(state', o) = func i state

out = run func state' input

#### State behaves like an accumulator

State behaves like an accumulator

- This is just a quick example of how we can simulate the mealy machine

- It sort of behaves like MapAccumN

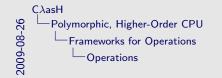

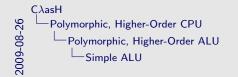

- Small Polymorphic, Higher-Order CPU

- Each function is turned into a hardware component

- Use of state will be simple

- Swala L

#### Small Polymorphic, Higher-Order CPU

# Each function is turned into a hardware component

Use of state will be simple

See a we

# Small Polymorphic, Higher-Order CPU Each function is turned into a hardware component Use of state will be simple

Mar Lauke

# Small Polymorphic, Higher-Order CPU Each function is turned into a hardware component Use of state will be simple

Real and

Small Polymorphic, Higher-Order CPU

Each function is turned into a hardware component

Use of state will be simple

Small Use Case

- Small "toy"-example of what can be done in  $\mathsf{C}\lambda\mathsf{asH}$

- Show what can be translated to Hardware

- Put your hardware glasses on: each function will be a component

- Use of state will be kept simple

#### Imports

Import all the built-in types, such as vectors and integers:

import CLasH.HardwareTypes

-Sugges

Import annotations, helps  $C\lambda$ asH to find top-level component:

import CLasH. Translator. Annotations

#### Imports

#### Import all the built-in types, such as vectors and integers:

#### import CLasH.HardwareTypes

2-2-3-L

Import annotations, helps  $C\lambda$ asH to find top-level component:

import CLasH. Translator. Annotations

#### Imports

Import all the built-in types, such as vectors and integers:

import CLasH.HardwareTypes

State Les

Import annotations, helps  $C\lambda$ asH to find top-level component:

import CLasH. Translator. Annotations

- The first input is always needed, as it contains the builtin types

- The second one is only needed if you want to make use of Annotations

and a let

#### First we define some ALU types:

```

type Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a

type Opcode = Bit

```

#### And some Register types:

AR ALL

**type** RegBank s a = Vector (s + D1) a **type** RegState s a = State (RegBank s a)

And a simple Word type:

**type** Word = SizedInt D12

First we define some ALU types:

**type**  $Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a$ **type** Opcode = Bit

And some Register types:

**type**  $RegBank \ s \ a = Vector \ (s + D1) \ a$ **type**  $RegState \ s \ a = State \ (RegBank \ s \ a)$

And a simple Word type:

type Word = SizedInt D12

First we define some ALU types:

**type**  $Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a$ **type** Opcode = Bit

And some Register types:

No. of Concession, Name

**type**  $RegBank \ s \ a = Vector \ (s + D1) \ a$ **type**  $RegState \ s \ a = State \ (RegBank \ s \ a)$

And a simple Word type:

**type** *Word* = *SizedInt D12*

|                                                                           | Type definitions |

|---------------------------------------------------------------------------|------------------|

| we define some ALU types:                                                 |                  |

| $Op \ s \ a = a \rightarrow Vector \ s \ a \rightarrow a$<br>Opcode = Bit |                  |

| ome Register types:                                                       |                  |

| RegBank s a = Vector (s + D1) a<br>RegState s a = State (RegBank s a)     |                  |

| simple Word type:                                                         |                  |

| Word = SizedInt D12                                                       |                  |

type type And i

type

- The first type is already polymorphic, both in size, and element type

- It's a small example, so Opcode is just a Bit

- State has to be of the State type to be recognized as such

- SizedInt D12: One concrete type for now, to make the signatures smaller

We make a primitive operation:

And a le

primOp ::  $(a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$ primOp f  $a \ b = a \ f' \ a$

We make a vector operation:

$vectOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$  $vectOp \ f \ a \ b = foldl \ f \ a \ b$

#### We make a primitive operation:

and the

$primOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$  $primOp \ f \ a \ b = a \ f' \ a$

#### We make a vector operation:

$vectOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$  $vectOp \ f \ a \ b = foldl \ f \ a \ b$

We make a primitive operation:

primOp ::  $(a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$ primOp f a b = a 'f' a

We make a vector operation:

$vectOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$  $vectOp \ f \ a \ b = foldl \ f \ a \ b$

We make a primitive operation:

primOp ::  $(a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$ primOp f a b = a 'f' a

We make a vector operation:

vectOp ::  $(a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$ vectOp f a b = foldI f a b

We make a primitive operation:  $primOp :: (a \rightarrow a \rightarrow a) \rightarrow Op \ s \ a$   $primOp \ f \ a \ b \rightarrow s'f' \ a$ We make a vector operation:

vectOp ::  $(a \rightarrow a \rightarrow a) \rightarrow Op s a$ vectOp f a b = fold! f a b

We support Higher-Order Functionality

- These are just frameworks for 'real' operations

- Notice how they are High-Order functions

Operations

## Simple ALU

#### We define a polymorphic ALU:

$\begin{array}{l} alu :: \\ Op \ s \ a \rightarrow \\ Op \ s \ a \rightarrow \\ Op code \rightarrow a \rightarrow Vector \ s \ a \rightarrow a \\ alu \ op1 \ op2 \ Low \ a \ b = op1 \ a \ b \\ alu \ op1 \ op2 \ High \ a \ b = op2 \ a \ b \end{array}$

#### We support Patter Matching

# Simple ALU

#### We define a polymorphic ALU:

$\begin{array}{l} alu :: \\ Op \ s \ a \rightarrow \\ Op \ s \ a \rightarrow \\ Op code \rightarrow a \rightarrow Vector \ s \ a \rightarrow a \\ alu \ op1 \ op2 \ Low \ a \ b = op1 \ a \ b \\ alu \ op1 \ op2 \ High \ a \ b = op2 \ a \ b \end{array}$

## We support Patter Matching

| Ne define a polymorphic ALU:                                    |  |

|-----------------------------------------------------------------|--|

| aluti                                                           |  |

| Op s a →                                                        |  |

| Op s a →                                                        |  |

| $Opcode \rightarrow a \rightarrow Vector \ s \ a \rightarrow a$ |  |

| alu op1 op2 Low a b = op1 a b                                   |  |

| alu op1 op2 High a b = op2 a b                                  |  |

|                                                                 |  |

| We support Patter Matching                                      |  |

|                                                                 |  |

Simple ALU

- Alu is both higher-order, and polymorphic

- We support pattern matching

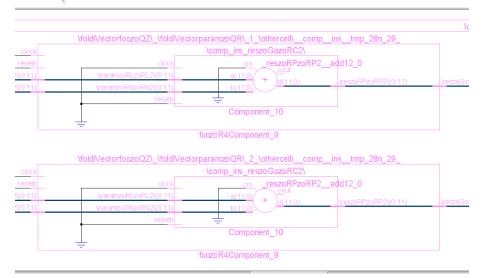

## Register Bank

#### Make a simple register bank:

```

\begin{array}{ll} \textit{registerBank}::\\ (Some \ \textit{context...}) \Rightarrow (\textit{RegState } s \ a) \rightarrow a \rightarrow \textit{RangedWord } s \rightarrow \textit{RangedWord } s \rightarrow \textit{RangedWord } s \rightarrow \textit{Bit} \rightarrow ((\textit{RegState } s \ a), a) \\ \textit{registerBank} \ (\textit{State } mem) \ data\_in \ \textit{rdaddr } wraddr \ wrenable = \\ ((\textit{State } mem'), data\_out) \\ \textit{where} \\ data\_out = mem \ ! \ \textit{rdaddr} \\ mem' \ | \ wrenable \equiv \textit{Low} = mem \\ & | \ \textit{otherwise} & = \textit{replace } mem \ wraddr \ data\_in \\ \end{array}

```

### We support Guards

$C\lambda$ asH - From Haskell To Hardware

## Register Bank

#### Make a simple register bank:

```

\begin{array}{ll} \textit{registerBank}::\\ (Some \ \textit{context...}) \Rightarrow (\textit{RegState } s \ a) \rightarrow a \rightarrow \textit{RangedWord } s \rightarrow \textit{RangedWord } s \rightarrow \textit{RangedWord } s \rightarrow \textit{Bit} \rightarrow ((\textit{RegState } s \ a), a) \\ \textit{registerBank} \ (\textit{State } mem) \ data\_in \ \textit{rdaddr } wraddr \ wrenable = \\ ((\textit{State } mem'), \ data\_out) \\ \textit{where} \\ \textit{data\_out = } mem \ ! \ \textit{rdaddr} \\ \textit{mem'} \ \textit{wrenable} \equiv \textit{Low} = mem \\ & \ \textit{otherwise} \ = \textit{replace } mem \ wraddr \ data\_in \\ \end{array}

```

## We support Guards

$C\lambda$ asH - From Haskell To Hardware

We support Guards

- RangedWord runs from 0 to the upper bound

- mem is statefull

- We support guards

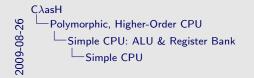

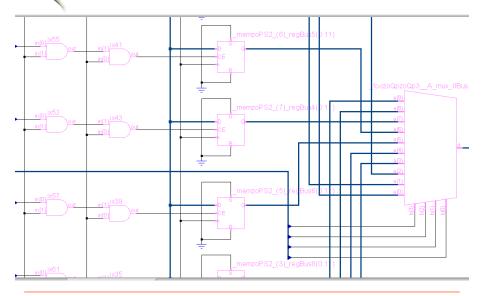

# Simple CPU

#### Combining ALU and register bank:

- {-#ANN actual\_cpu TopEntity#-} actual\_cpu :: (Opcode, Word, Vector D4 Word, RangedWord D9, Dage (March D2 Di) \_\_\_\_\_ Dage (Letter D2 March

- RangedWord D9, Bit)  $\rightarrow$  RegState D9 Word  $\rightarrow$  (RegState D9 Word, Word)

- actual\_cpu (opc, a, b, rdaddr, wraddr, wren) ram = (ram', alu\_out)

where

- alu\_out = alu (primOp (+)) (vectOp (+)) opc ram\_out b

(ram', ram\_out) = registerBank ram a rdaddr wraddr wren

#### Annotation is used to indicate top-level component

# Simple CPU

#### Combining ALU and register bank:

{-#ANN actual\_cpu TopEntity#-}

actual\_cpu ::

(Opcode, Word, Vector D4 Word, RangedWord D9,

RangedWord D9, Bit) → RegState D9 Word →

(RegState D9 Word, Word)

actual\_cpu (opc, a, b, rdaddr, wraddr, wren) ram = (ram', alu\_out)

#### where

alu\_out = alu (primOp (+)) (vectOp (+)) opc ram\_out b

(ram', ram\_out) = registerBank ram a rdaddr wraddr wren

## Annotation is used to indicate top-level component

September 3, 2009

# Simple CPU

#### Combining ALU and register bank:

$\{-\#ANN \ actual\_cpu \ TopEntity \#-\}$ actual\\_cpu :: (Opcode, Word, Vector D4 Word, RangedWord D9, RangedWord D9, Bit)  $\rightarrow$  RegState D9 Word  $\rightarrow$ (RegState D9 Word, Word) actual\\_cpu (opc, a, b, rdaddr, wraddr, wren) ram = (ram', alu\_out) where

alu\_out = alu (primOp (+)) (vectOp (+)) opc ram\_out b

(ram', ram\_out) = registerBank ram a rdaddr wraddr wren

## Annotation is used to indicate top-level component

September 3, 2009

- Annotation is used to indicate top-level component

- We use the new Annotion functionality to indicate this is the top level

- the primOp and vectOp frameworks are now supplied with real functionality, the plus (+) operations

- No polymorphism or higher-order stuff is allowed at this level.

- Functions must be specialized, and have primitives for input and output

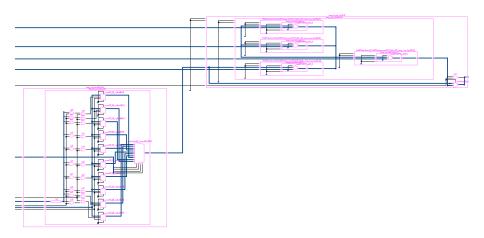

- We will simulate the small CPU from earlier

- Translate that CPU code to VHDL

- Simulate the generated VHDL

- See the hardware schematic of the synthesized VHDL

AND SALL

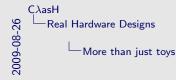

- We designed a matrix reduction circuit

- Simulation results in Haskell match VHDL simulation results

- Synthesis completes without errors or warnings

- It runs at half the speed of a hand-coded VHDL design

- Swala we

## We designed a matrix reduction circuit

- Simulation results in Haskell match VHDL simulation results

- Synthesis completes without errors or warnings

- It runs at half the speed of a hand-coded VHDL design

See a Le

- We designed a matrix reduction circuit

- Simulation results in Haskell match VHDL simulation results

- Synthesis completes without errors or warnings

- It runs at half the speed of a hand-coded VHDL design

and a we

- We designed a matrix reduction circuit

- Simulation results in Haskell match VHDL simulation results

- Synthesis completes without errors or warnings

- It runs at half the speed of a hand-coded VHDL design

See a le

- We designed a matrix reduction circuit

- Simulation results in Haskell match VHDL simulation results

- Synthesis completes without errors or warnings

- It runs at half the speed of a hand-coded VHDL design

AND IN LOW

We designed a matrix reduction circuit Simulation results in Hackell match VHDL simulation results Synthesis completes without errors or warnings It runs at half the speed of a hand-coded VHDL design

More than just toys

- Toys like the poly cpu one are good to give a quick demo

- But we used  $C\lambda$ asH to design 'real' hardware

- Reduction circuit sums the numbers in a row of a (sparse) matrix

- Half speed is nice, considering we don't optimize for speed

- In three simple steps really:

- No Effort:

- GHC API Parses, Typechecks and Desugars the Haskell code

- Hard:

-See and

- Transform resulting Core, GHC's Intermediate Language, to a normal form

- Easy:

- Translate Normalized Core to synthesizable VHDL

## In three simple steps really:

- No Effort:

- GHC API Parses, Typechecks and Desugars the Haskell code

- Hard:

-See au

- Transform resulting Core, GHC's Intermediate Language, to a normal form

- Easy:

- Translate Normalized Core to synthesizable VHDL

- In three simple steps really:

- No Effort: GHC API Parses, Typechecks and Desugars the Haskell code

- Hard:

See Law

- Transform resulting Core, GHC's Intermediate Language, to a normal form

- Easy:

- Translate Normalized Core to synthesizable VHDL

- In three simple steps really:

- No Effort:

GHC API Parses, Typechecks and Desugars the Haskell code

Hard:

Transform resulting Core, GHC's Intermediate Language, to a normal form

Easy:

Translate Normalized Core to synthesizable VHDL

- In three simple steps really:

- No Effort:

GHC API Parses, Typechecks and Desugars the Haskell code

Hard:

Transform resulting Core, GHC's Intermediate Language, to a normal form

Easy:

Translate Normalized Core to synthesizable VHDL

- Here is a quick insight as to how WE translate Haskell to Hardware

- You can also use TH, like ForSyDe. Or traverse datastructures, like

- We're in luck with the GHC API update of 6.10 and onwards

- Normal form is a single lamda and a let expression, every let binder is a simple assignment

# Some final words

- Still a lot to do: translate larger subset of Haskell

- Real world prototypes can be made in CλasH

- CλasH is another great example of how to bring functional expressivity to hardware designs

# Thank you for listening

CλasH Clone URL: git://github.com/christiaanb/clash.git

C<sub>λas</sub>H - From Haskell To Hardware

May Lo

September 3, 2009

## Complete signature for registerBank

```

registerBank ::

(NaturalT s

, PositiveT (s + D1)

,((s + D1) > s)~True)) \Rightarrow

(RegState s a) \rightarrow a \rightarrow RangedWord s \rightarrow

RangedWord s \rightarrow Bit \rightarrow ((RegState s a), a)

```

-Sea and

-Support

-5-23-4